IP平台

目标:帮助IC设计企业提高设计效率、提升设计产品档次、降低产品开发风险

。

主要工作:

1)与境内外IP组织、产品提供商等建立业务合作关系,为设计企业提供IP复用、验证服务及IP整合服务;

2)为本地设计企业提

IP信息共享平台;

3)帮助企业开展IP硬化及推广IP商业化服务,以及做好企业之间

IP交易;

4)联系相关组织与单位举行IP核的标准化指导性讲座活动(以推动IP核市场化步伐,完善IP标准化的工作);

5)通过信息传递对企业产品进行宣。

IP服务中心简介

IP服务中心立足本地IP资源,开拓广泛的国内国际合作资源,建立IP开发、交易、共享、应用的服务体系,为本地区的IC设计企业提供全方位的IP服务,帮助设计企业提高设计效率、提升设计产品档次、降低产品开发风险。

关 于 IP

设计能力和制造能力存在着距离:按照摩尔定律,芯片制造能力大约每年增长58%;随着集成电路规模和复杂性的增大,进入90年代中后期,集成电路设计能力的年增长比率约为21%,滞后于制造技术能力的提高,二者间存在差距。弥补设计生产效率和芯片密度之间的差距争取第一个进入市场最有效的方法是重复使用已有的设计(设计再利用)或虚拟器件(VC)即IP核技术。

硬件厂商提供的不再是真实的单个实元件芯片,而是IP(intellectual properties)模块,包括软IP、固化(firm) IP和硬IP三种类型。其中,软IP是HDL描述,固化IP是指门级网表描述,硬IP是指实现到物理版图的硅块(silicon block)。此时,系统设计人员通过利用供应商提供的IP模块来设计实现整个系统,这些被提供的IP模块也称为虚拟元件(virtual component)。

软件IP:软件IP可以定义为实现特定功能的软件。一般称为中间软件、固件、驱动软件等。其中有语音合成识别、MPEG(Moving Picture Experts Group)信号处理、加密算法、显示驱动、用于半导体IP的各种驱动软件及固件等。OS及嵌入式实时操作系统也可以说是一种IP。

硅知识产权的出现是集成电路设计产业分工的结果,它使一些公司可以专注于自己的技术特长,提供不同类型的、经过验证的硅知识产权,而另一些公司在复用这些硅知识产权的基础上设计系统芯片。这种设计方法的出现显著加快了芯片开发速度,缩短了产品上市周期,使更大规模、更多功能、更高集成度的芯片设计成为可能。业界专家认为,硅虚拟原型将推动寄存器传输级(RTL)的设计自动化进程。专有知识产权(IP:Intellectual Property)核的设计再利用是保证系统级芯片开发效率和质量的重要手段。

实现SOC有两种做法:一种是从ASSP走向SOC,一种是将CPU、DSP放进PLD或FPGA中支持用户实现SOC。不管采用哪种做法,必须解决的课题是发展IP或取得IP使用权。

硬"核"的设计规则和版图固定,生产适应性窄但性能能够保证:软"核"版图设计自由度高但难以严密保证性能;固件"核"介于二者之间。

设计资产(IP)再利用需要解决的课题是:可重用设计技术和设计工具开发、设计标准化和IP评价方法、流通市场的形成、IP保护技术等。

IP核的标准化团体美国VSIA(Virtual Socket Interface A11iance)已经制定出IP核间的通信规约SLD(System-Level Interface Behavioral Documentation Standard Ver.11.0) 并通过www开始向其成员发布。SLD11.0规定了在多个抽象级上IP"核"间的通信标准,使IP"核"自身和接口部分容易分离开来。2000年6月借助互连网进行IP交易的英国VCX(Virtual Components Exchange)的成员企业和团体己达到36家。日本由东芝、三菱商事、日经BP等12家出资成立的IPTC从2000年11月开始进行实验,2001年4月开始正式IP核交易。

模拟电路IP化滞后于数字IP。模拟IP装入SOC的最大问题是电源电压。另外工艺条件、器件结构不同也是课题。最新的进展表明,可将模拟版图IP化的技术已经问世。HDLAMS(Analog and Mixed Signal)记述语言的标准化,使模拟电路IP化及其流通成为可能。模拟IP有用于混合仿真的动作模型、可进行模拟合成/最佳化的网表IP和完成版图设计的硬IP等3种。

面向可编程器件的IP。如只通过选择功能及地址宽度和存储器尺寸等就可以灵活实现与应用最吻合的处理器结构的柔性RISC处理器以及以太网MAC等通信电路,误码纠借用Reed-Solomon编解码DSP,PCI总线接口IP等。面向设计开发时间短及多品种的可编程器件和设计资产IP相结合可使二者的优点相乘。可以大幅度缩短开发周期、灵活的设计变更,提高附加价值,降低开发风险和成本。

服 务 内 容

成立本地拥有自主知识产权IP联盟;完善IP评价条件与评估程序,HardIP技术标准以及IP硬化管理办法;建立本地以有IP的信息发布、搜索和咨询以及共享、交换、交易服务平台;完成以有IP的标准化及认证;IP工艺转移服务及后端设计IP整合服务;对于拥有自主知识产权的优秀IP提供硅验证服务;开展IP开发和管理技术培训、组织技术交流活动。

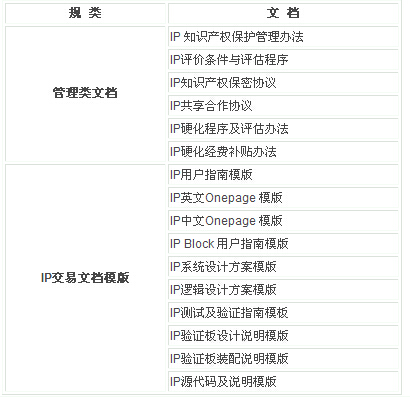

IP复用管理规范文档

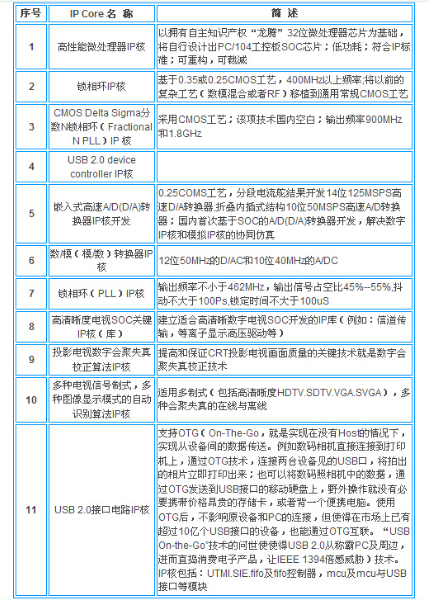

IP 资 源

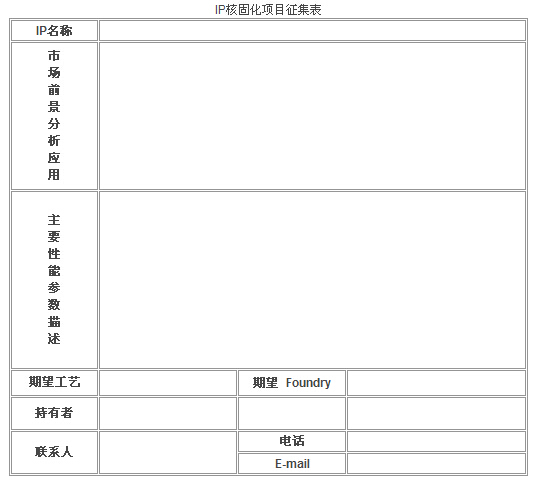

IP征集表格

IP评估与验证

因为IP许可的成本很高,IP用户必须对IP内核进行无风险的试用编译,以验证开发者所宣称的功能性、密度和性能。开放式内核试用必须使用户得到足够的信 息,以决定是否购买许可,同时又不可能在未付许可费的情况下将内核用于商业用途。因而有必要让设计师在购买IP之前对其进行充分评估,同时又保护内核及其源代码的知识产权,以防盗用。

联系方式:

联系人:赵城 电话: 029-88328230-8002 电子邮件: zhaocheng@xaic.com.cn

Copy right©2007:All Reserved. 西安集成电路设计专业孵化器有限公司

办公地址:陕西省西安市高新技术产业开发区科技二路77号光电园二层北 办公电话:029-88328230 传真:029-88316024

陕ICP备 19002690号

![]() 陕公安网备 61019002000194号

陕公安网备 61019002000194号